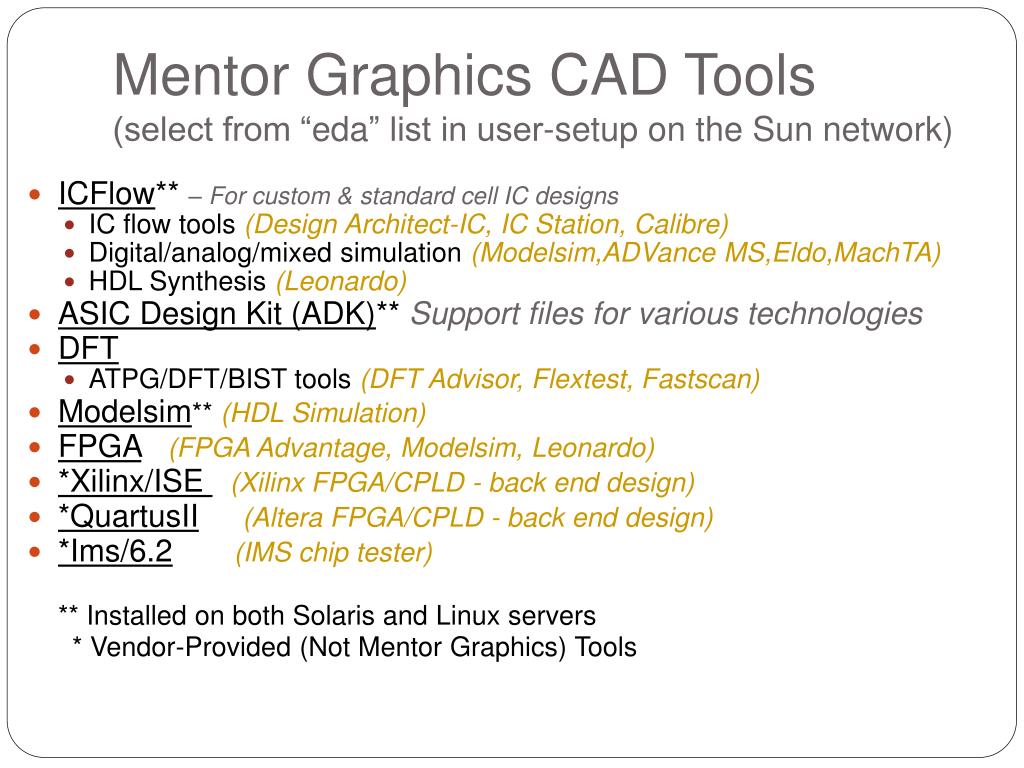

I mean, hey, they're just languages, and once you've learned a dozen or so, they all blend together. So, although you're having fun playing with Python, perhaps the time would be better spent playing with SystemVerilog, VHDL, or Tcl. However, there's very little need for manipulating the waveforms after-the-fact. Sure, I'll create figures for sections of waveforms to show that the interface implements the timing 'per the datasheet' of whatever I'm interfacing to. Well, in my experience, I don't care what the waveforms look like after the testbench has been run in the simulator and all tests have passed. Modelsim - Object not logged & no signal data while simulating verilog clock divider code. > I do not have access to other simulators.

This would probably be best for "proper" design flows, but maybe a little in-flexible for a hobbyist poking around :-) I am using modelsim Altera starter edition 10.1.b. A warning in not mandatory, because the port was coerced > Iztok JerasI've seen some recommended methods for using VHDL constructs to automatically write their simulated data out to a file, from what I've seen you have to add a construct for each signal you want to probe. We encourage you to take an active role in the Forums by answering and commenting to any questions that you are able to.

TBH, I'm much more familiar with Python (& Matplotlib) than I am with TCL and SystemVerilog. The Verification Community is eager to answer your UVM, SystemVerilog and Coverage related questions. No "Big Picture" yet, at this point I'm just trying to see what kind of connectivity is possible between different tools.

0 kommentar(er)

0 kommentar(er)